## **FASTSERIES**

FASTIMAGE 1300 HARDWARE USER'S MANUAL

# FAST CAPTURE FAST PROCESSING FAST RESULTS

FASTSERIES PCI BOARD

FAST SERIES PMCs

FastVision

FastImage 1300

FastFrame 1300

FastMem Fast4 1300 Fast I/O 1300

#### COPYRIGHT NOTICE

#### Copyright ã 2002 by Alacron Inc.

All rights reserved. This document, in whole or in part, may not be copied, photocopied, reproduced, translated, or reduced to any other electronic medium or machine-readable form without the express written consent of Alacron Inc.

Alacron makes no warranty for the use of its products, assumes no responsibility for any error, which may appear in this document, and makes no commitment to update the information contained herein. Alacron Inc. retains the right to make changes to this manual at any time without notice.

Document Name FastImage 1300 Hardware User's Manual

Document Number: 30002-00176

Revision History: 2.0 June 4, 2002

#### Trademarks:

Alacrona is a registered trademark of Alacron Inc.

AltiVecÔ is a trademark of Motorola Inc.

Channel LinkÔ is a trademark of National Semiconductor

**CodeWarrior**â is a registered trademark of Metrowerks Corp.

FastChannelâ is a registered trademark of Alacron Inc.

FastSeriesâ is a registered trademark of Alacron Inc.

Fast4â, FastFrame 1300â, FastImageâ, FastI/Oâ, and FastVisionâ are registered trademarks of Alacron Inc.

**FireWire**Ô is a registered trademark of Apple Computer Inc.

**3M**Ô is a trademark of 3M Company

MS DOSa is a registered trademark of Microsoft Corporation

**SelectRAM**Ô is a trademark of Xilinx Inc.

**Solaris**Ô is a trademark of Sun Microsystems Inc.

**TriMedia**Ô is a trademark of Philips Electronics North America Corp.

Unixâ is a registered trademark of Sun Microsystems Inc.

**Virtex**Ô is a trademark of Xilinx Inc.

Windows Ô, Windows 95Ô, Windows 98Ô, Windows 2000Ô, and Windows NTÔ are trademarks of Microsoft Corporation

#### All trademarks are the property of their respective holders.

Alacron Inc. 71 Spit Brook Road, Suite 200 Nashua, NH 03060 USA

Telephone: 603-891-2750 Fax: 603-891-2745

Web Site: http://www.alacron.com/

Email: <u>sales@alacron.com</u> or <u>support@alacron.com</u>

## TABLE OF CONTENTS

| Table o         | ght Notice  f Contents  Figures & Tables       | ii<br>iii |

|-----------------|------------------------------------------------|-----------|

|                 | Alacron Manuals                                | Vi<br>Vi  |

|                 |                                                |           |

| I. IN           | TRODUCTION                                     | 1         |

| A.              | FastImage 1300                                 | 1         |

| В.              | Processors and Memory                          | 1         |

| C.              | Analog and Digital Input                       | 2         |

| 1.              | Analog Input                                   | 2         |

| 2.              | Digital Input                                  | 2         |

| 3.              | Digital Control Inputs                         |           |

| 4.              | Digital Control Outputs                        | 3         |

| D.              | Other Inputs and Outputs                       | 3         |

| 1.              | Analog Output                                  |           |

| 2.              | FastChannel Digital Input/Output               |           |

| 3.              | Channel Link Input/Output                      |           |

| TC.             | PMC Daughter Cards                             |           |

| E.              |                                                |           |

| F.              | Local PCI Bus                                  |           |

| II.             | THEORY OF OPERATION                            |           |

| A.              | Camera Types                                   | 5         |

| В.              | Analog Video Input                             | 5         |

| 1.              | NTSC/PAL Composite and S-Video Component Input | 6         |

| 2.              | Monochrome and RGB Analog Video Input          | 7         |

| C.              | Digital Input                                  | 7         |

| 1.              | Digital Control Inputs                         |           |

| 2.              | Camera Controls                                |           |

| D.              | FPGA-Based Front End                           | 0         |

| <b>ט.</b><br>1. | FPGA Run States                                |           |

| 2.              | Input Signals from Line Cameras to FPGA        |           |

| 3.              | Input Signals from Frame Cameras to FPGA       |           |

| 4.              | NTSC/PAL/S-Video Input Signals                 |           |

| 5.              | Data Reordering                                |           |

| 6.              | Image Distribution                             |           |

| 7.              | Data Valid Signals                             |           |

| Ε.              | Digital Crosspoint Switch                      | 13        |

| F.              | Processors and Memory                          |           |

| 1.              | TriMedia Processors                            |           |

| 2.              | Local SDRAM                                    |           |

| 3.              | Video Data Paths                               |           |

| 4.              | Local PCI Bus                                  |           |

| 5.              | Interprocessor Communication                   |           |

| 6.              | Audio Input and Output                         |           |

| 7.              | Interrupts                                     |           |

| 8.              | TriMedia Configuration EEPROM                  | 20        |

| 9.              | Peripheral Controls                            | 20        |

| G.        | FastChannel Digital Input/Output                                  | 20 |

|-----------|-------------------------------------------------------------------|----|

| н.        | Analog Output                                                     | 22 |

| I.        | PCI-PCI Bridge                                                    | 22 |

| J.        | PMC Slots                                                         | 23 |

| K.        | CPLD                                                              |    |

| L.        | UART and Serial Port                                              |    |

| M.        | Power                                                             | 23 |

| N.        | Clock Distribution                                                | 24 |

| 1.        |                                                                   |    |

| III.      | CONNECTORS AND JUMPERS                                            | 28 |

| Α.        | Connectors                                                        |    |

| 1.        |                                                                   |    |

| 2.        |                                                                   |    |

| 3.        |                                                                   |    |

| 4.<br>5.  |                                                                   |    |

| 5.<br>6.  |                                                                   |    |

| 7.        |                                                                   |    |

| 7.        |                                                                   |    |

| В.        | Jumpers                                                           |    |

| 1.        |                                                                   |    |

| 2.        |                                                                   |    |

| 3.        |                                                                   |    |

| 4.        |                                                                   |    |

| 5.        | . P16                                                             | 34 |

| IV.       | FASTIMAGE 1300 CABLES                                             | 35 |

| A.        | Cable Summary                                                     | 35 |

| В.        | Power Cables                                                      | 35 |

| <b>C.</b> | Digital Input Cable                                               | 35 |

| D.        | Analog Input Cable                                                | 37 |

| E.        | ChannelLink/TV/RS-232 Cable                                       | 38 |

| F.        | NTSC/TV Out Cable                                                 | 39 |

| G.        | FastChannel Digital I/O Output (J4, J5)                           | 39 |

| V.        | PROGRAMMING, CONFIGURATION, AND TEST                              | 40 |

| A.        | I2C Bus                                                           | 40 |

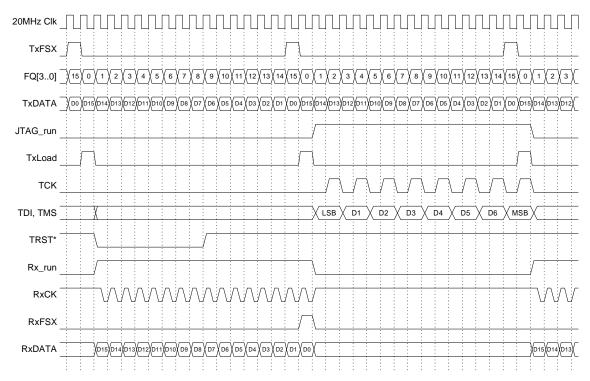

| В.        | V.34 SSI Interface (TM1 to CPLD)                                  | 40 |

| 1.        |                                                                   |    |

| 2.        |                                                                   |    |

|           |                                                                   |    |

| <b>C.</b> | JTAG Chains                                                       |    |

| 1.        |                                                                   |    |

| 2.        |                                                                   |    |

| 3.        | . JTAG Chain #3 – CPLD, FPGA1, FPGA2, Crosspoint FPGAs, and IQ32B | 43 |

| VI.       | CPLD SPECIFICATION                                                | 44 |

| Λ         | V 34 SSI Interface                                                | 44 |

| В.           | JTAG Interface                                           | 45 |

|--------------|----------------------------------------------------------|----|

| С.           | External Five-Wire Interface                             | 45 |

| D.           | PCI Bus Secondary Clock Mask                             | 46 |

| E.           | Low-Speed Timing Functions                               | 46 |

| <b>F.</b> 1. | CPLD Programming Requirements  Address (Hex) Description |    |

| VII.         | UART Specification                                       | 51 |

| Α.           | Purpose                                                  | 51 |

| В.           | Features                                                 | 51 |

| С.           | I <sup>2</sup> C Address                                 | 51 |

| D.           | Interrupts                                               | 51 |

| Е.           | Register descriptions                                    | 52 |

| 1.           | Subaddress 00, Write – UART Control Register             | 52 |

| 2.           | ,                                                        |    |

| 3.           | ,                                                        |    |

| 4.           |                                                          |    |

| 5.<br>6.     | ,                                                        |    |

| 7.           |                                                          |    |

| VIII.        | Specifications                                           | 56 |

| Α.           | Processors                                               | 56 |

| В.           | NTSC/PAL Composite Video Capture                         | 56 |

| C.           | Analog Video Capture                                     | 56 |

| D.           | Digital Video Capture                                    | 57 |

| <b>E.</b>    | Digital Video Output                                     | 57 |

| F.           | Camera Control                                           | 57 |

| G.           | Analog Video Output                                      | 57 |

| н.           | Monitor Output                                           | 58 |

| I.           | PCI Interface                                            | 58 |

| J.           | PMC Interface                                            | 58 |

| IX.          | TROUBLESHOOTING                                          | 59 |

| <i>X</i> .   | ALACRON TECHNICAL SUPPORT                                | 60 |

| A.           | Contacting Technical Support                             | 60 |

| В.           | Returning Products for Repair or Replacements            |    |

| C            | Reporting Rugs                                           | 62 |

## **MANUAL FIGURES & TABLES**

| FIGURE | PAGE | SUBJECT                       | TABLE | PAGE | SUBJECT                        |

|--------|------|-------------------------------|-------|------|--------------------------------|

| 1      | 1    | Block Diagram of the FI1300   | 1     | 6    | Composite Analog Video Inputs  |

| 2      | 5    | Data Flow of the FastImage    | 2     | 7    | 8 Bit Analog Input Channel     |

| 3      | 6    | Analog Video Input            | 3     | 21   | FastChannel Interface Controls |

| 4      | 7    | Digital Video Input           | 4     | 21   | I/O Expander Registers         |

| 5      | 9    | Camera Control Output Signal  | 5     | 26   | IQ32B Signals                  |

| 6      | 10   | Front End Comp & Data Flow    | 6     | 29   | A/D Input Connector J1A/J1B    |

| 7      | 11   | Line Camera Input Signals     | 7     | 30   | Analog Output/CL/RS232 Conn.   |

| 8      | 11   | Digital Frame Camera Input S. | 8     | 31   | FastChannel Digital I/O Conn.  |

| 9      | 12   | NTSCPAL/S Video Input S.      | 9     | 32   | PMC-PN4 Connectors J1/J3       |

| 10     | 14   | Main Crosspoint Switch Conn.  | 10    | 32   | Test Connector P10             |

| 11     | 16   | Processors and Memory         | 11    | 33   | Test Connector P11             |

| 12     | 17   | Message Passing Connection    | 12    | 33   | Test Connector P12             |

| 13     | 18   | Audio Connections             | 13    | 33   | Jumper P3                      |

| 14     | 19   | Interrupts                    | 14    | 34   | Jumper P9                      |

| 15     | 20   | FastChannel Input/Output      |       | 34   | Jumper P14                     |

| 16     | 22   | 22 Analog Output              |       | 34   | Jumper P16                     |

| 17     | 25   | IQ32B Clock Distribution      | 17    | 36   | Digital Input Cable, DSUB37 P2 |

| 18     | 28   | FI1300 Front Panel Bracket    | 18    | 37   | Digital Input Cable, DSUB37 P3 |

| 19     | 40   | Configuration & Control       | 19    | 38   | Analog Input Cable             |

| 20     | 45   | V.34 Interface Timing         | 20    | 38   | NTSC/S Video Conn P2 & P3      |

| 21     | 47   | Low-Speed Timing Signals, Ex  | 21    | 38   | RS-232 Connector P4            |

| 22     | 47   | Low-Speed Timing Signals, Fr  | 22    | 39   | SVGA (RGB) Output Conn P5      |

|        |      |                               | 23    | 48   | Control Register Bits          |

|        |      |                               | 24    | 49   | Crosspoint Control register    |

## **OTHER ALACRON MANUALS**

Alacron manuals cover all aspects of FastSeries hardware and software installation and operation. Call Alacron at 603-891-2750 and ask for the appropriate manuals from the list below if they did not come in your FastSeries shipment.

| • | 30002-00146 | FastImage and FastFrame HW Installation for PCI Systems       |

|---|-------------|---------------------------------------------------------------|

| • | 30002-00148 | ALFAST Runtime Software Programmer's Guide & Reference        |

| • | 30002-00150 | FastSeries Library User's Manual                              |

| • | 30002-00153 | Fast I/O Hardware User's Manual                               |

| • | 30002-00155 | FastMem Hardware User's Manual                                |

| • | 30002-00162 | FOIL - FastSeries Object Imaging Library User's Manual        |

| • | 30002-00169 | ALRT Runtime Software Programmer's Guide & Reference          |

| • | 30002-00170 | ALRT, ALFAST & FASTLIB Software Installation Manual for Linux |

| • | 30002-00171 | ALRT, ALFAST, & FASTLIB Software Installation for Windows NT  |

| • | 30002-00172 | FastImage 1300 Hardware User's Manual                         |

| • | 30002-00173 | FastMem Programmer's Guide & Reference                        |

| • | 30002-00174 | FastMem Hardware Installation Manual                          |

| • | 30002-00180 | Fast4 1300 Hardware User's Manual                             |

| • | 30002-00184 | FastSeries Getting Started Manual                             |

| • | 30002-00185 | FastVision Hardware Installation Manual                       |

| • | 30002-00186 | FastVision Software Installation Manual                       |

## I. INTRODUCTION

#### A. Fastlmage 1300

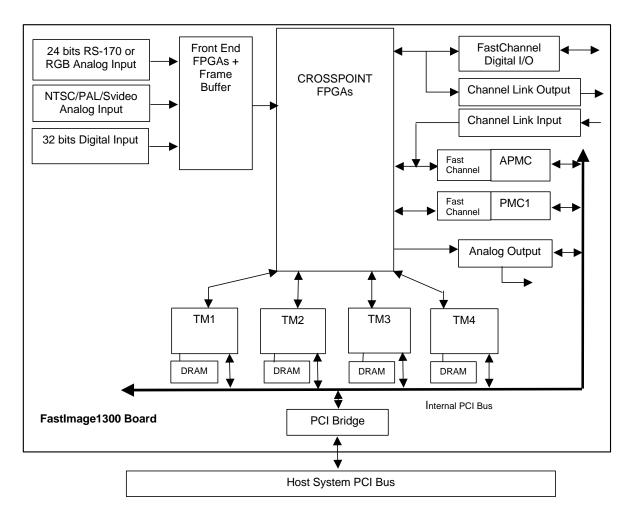

The FastImage1300 is an autonomous imaging system that can process up to four continuous video streams with minimal impact on the Host system. The FastImage1300 system consists of a main board with one to four TriMedia TM1300 PCI media processors and memory. Options include analog or digital input via a frame buffer, unbuffered digital I/O, Channel Link I/O, analog output, and one or two PMC daughter cards.

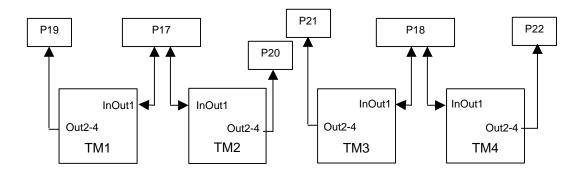

Figure 1. Block Diagram of the FI1300 Board in a PC Chassis

## B. <u>Processors and Memory</u>

The FastImage 1300 can be configured with one or four Trimedia 1300 DSP processors (TM1 through TM4). The crosspoint switch eliminates the need to bypass missing processors' video paths, however zero ohm resistors will be required to complete the JTAG data loop in one-CPU systems. Sensing resistors will also be included to allow the bridge chip to disable unused clock lines on the secondary PCI bus.

Reducing the number of processors also reduces the input bandwidth of the board. The total input bandwidth is limited to 80 MB/s per installed processor. Also, systems with just one processor will have one master clock output instead of two.

Each processor can have 8MB, 16MB, 32MB or 64MB of dedicated SDRAM. All TMs on a given board must have the same amount of SDRAM.

#### C. Analog and Digital Input

The board has four inputs, TAP1 through TAP4; each TAP consists of 8 bits data, 2 bits control, and pixel clock. A TAP can be configured for analog input or for digital input (but not both). TAP1 through TAP3 can be populated as either digital input or RS170 compatible analog input. TAP4 can be either digital input or composite analog input (NTSC/PAL/SECAM or S-Video).

Analog and digital video capture signals come in through the same dual 68-pin VHDCI connector, J1A/J1B. In order to save pins, analog and digital signals share pins, allowing only one or the other for each of the four input taps.

Inputs from the four TAPs go to the Front End FPGAs with their associated frame buffers, and then are routed via the crosspoint to the TriMedia or FastChannel.

#### 1. Analog Input

Four RS-170 level video inputs allow selection from four composite video sources. The same inputs can also be used in pairs to receive S-video signals. Note that only one composite/component video stream can be captured at one time. These inputs are multiplexed into a common converter (two converters in S-video mode). The primary TM1300 controls the input selection using the I<sup>2</sup>C bus to access the internal registers of the SAA7111A.

Three additional RS-170 level video inputs can be used to capture images from three additional monochrome cameras or one RGB camera. Sync detection circuitry for these inputs is very flexible, allowing the use of asynchronous reset cameras as well as interlaced or progressive area scan cameras and line scan cameras.

#### 2. Digital Input

Digital video input lines allow direct connection of digital line-scan or area-scan cameras of up to 32 bits. The 32 Digital data inputs are received by high-speed RS422 differential receivers whose outputs are run through the FPGA-based front end to standard I/O's on the crosspoint switch. The switch can then route these to the data inputs of the TM1300 processors or the digital video input port of the S3 Virge GX2.

All digital video data and control signals are differential RS-422 level signals with proper termination for twisted pair cable. High-speed line drivers and receivers are used on all digital signals, however the RS-422 standard was not designed for very high data rates. Thus the interface circuitry may limit the maximum practical data rate to considerably less than the 80 MHz video input bandwidth of the TriMedia chips unless the receivers are upgraded to the LVDS model. Industry standard pin-out devices are used for all RS422 receivers and drivers (26LS31 and 26LS32 footprint) to allow upgrade to faster parts as required. LVDS interface drivers and receivers are available as selective stuffing options.

#### 3. Digital Control Inputs

Four special clock inputs are provided. These inputs are received by high-speed RS422 differential receivers. The outputs of these receivers go to dedicated global clock inputs of the FPGA. Programmable clock polarity and input delay allow compensation for clock to data skew.

Eight additional control inputs are provided. These inputs are received by high-speed RS422 differential receivers. The outputs of these receivers go to the FPGA. These lines may be used for frame valid and line valid signals when attaching multiple cameras.

Four general purpose static inputs are provided. These inputs are received by RS422 differential receivers. The outputs of these receivers can be read directly by the primary TM1300 via the I<sup>2</sup>C bus.

#### 4. Digital Control Outputs

Two outputs are provided for line or frame start. These RS422 differential outputs are intended for uses with line scan or area scan cameras that require a scan start pulse. They are generated in the CPLD in response to external trigger inputs (after a programmed delay) or on command of the primary TM1300.

Two outputs are provided for exposure control. These RS422 differential outputs are intended for uses with line scan or area scan cameras, which require a scan, start pulse. They are generated in the CPLD in response to external trigger inputs (without a delay) or on command of the primary TM1300. Camera exposure time is controlled by the delay between these signals and the line / frame start signals.

Two master clock outputs are provided to generate a time base for cameras. These RS422 differential outputs are intended for use with line scan or area scan cameras, which require an external time base. They are generated by the primary and secondary TM1300's using the AI\_OSCLK outputs. Only one of these signals is available on the single processor model. These pins can generate any frequency from 1 Hz to 40 MHz in .07 Hz steps using the direct digital synthesizer of the TM1300. Nominal jitter on these outputs due to digital synthesis is 3.3 nanoseconds. This will be reduced to less than 1 nanosecond in the TM1300 when the improved mode is used. In TM1300 improved mode, the frequency resolution is 0.3 Hz.

Four general purpose static outputs are provided. These RS422 differential outputs can be written directly by the primary TM1300 via the I<sup>2</sup>C bus.

#### D. Other Inputs and Outputs

The system can be configured with analog output, FastChannel input/output, Channel Link input/output, or with no output.

#### 1. Analog Output

Analog output can drive the system SVGA display and also provide NTSC TV output to a monitor.

SVGA monitor signals go out through 68-pin high-density connector J2. Composite and S-video outputs, and the RS-232 port also share connector J2 and Channel Link.

Systems that have another video adapter in addition to the onboard S3-based SVGA can use the host's adapter and monitor to display video output in one or more possibly overlapping windows. The TM1300 supports this functionality directly via the image coprocessor unit. When using the onboard S3 SVGA, processed image data can be scaled and alpha blended as well.

#### 2. FastChannel Digital Input/Output

The FastChannel interface provides 32 bits of digital input and output directly to and from the crosspoint via connectors J4 and J5 on the top edge of the board. The interface includes 32 bits of RS422 or LVDS differential digital output drivers and receivers, with RS422 digital video control and clock inputs/outputs.

#### 3. Channel Link Input/Output

The FastImage1300 implements the 28-bit Channel Link digital I/O interface as an option. Compatible cameras or other input devices can be connected directly to the Channel Link inputs. Channel Link outputs may be connected to another FastImage1300 for high-speed inter-board communication.

#### E. PMC Daughter Cards

Two PMC slots connect to the FastImage internal PCI bus via standard PMC connectors and to the crosspoint switch via the Alacron FastChannel connector. Daughter cards from Alacron are available to extend the I/O, memory, or processing power of a FastImage board via the PMC slots and FastChannel.

- Fast4 daughter card supplies one to four additional TriMedia processors.

- FastIO daughter card supplies additional digital or analog I/O.

- FastMem daughter card supplies up to 512MB of global SDRAM.

Each of these products is described in its own documentation set.

#### F. Local PCI Bus

All other data into and out of the FastImage use the PCI bus. High-speed devices such as IEEE 1394 FireWire connect to the secondary PCI bus via the PMC expansion connectors. Additional devices can be connected to the host's primary PCI bus.

## II. THEORY OF OPERATION

This chapter describes the camera connections, internal data flow paths, and other functional components of the FastImage board.

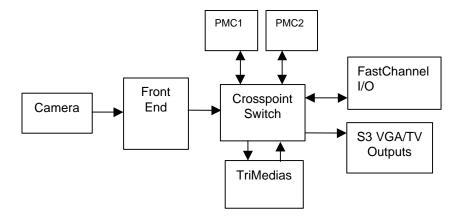

Figure 2. Data Flow in the FastImage

Input data from the camera is converted (as needed) into RGB or YUV digital data by the front end and distributed to the TriMedia processors via the crosspoint. Output data from the TriMedia goes via the crosspoint to the S3 SVGA/TV outputs, and can also be routed among the TriMedia and to and from PMC daughter cards. The FastChannel I/O connects directly to the crosspoint as a separate source or as a destination for TriMedia output.

#### A. Camera Types

A camera can be digital or analog, line or frame, single- or multi-tap. Common configurations are:

- Three 8-bit RS-170 cameras plus one NTSC/PAL/S-Video camera.

- Four 8-bit asynchronous digital cameras (quad single-tap)

- Two 16-bit digital cameras (dual two-tap)

- One 32-bit digital camera (single four-tap)

#### B. Analog Video Input

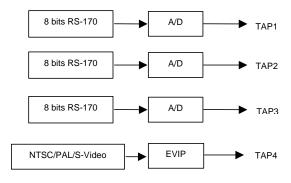

Analog video capture signals come in the dual 68-pin VHDCI connector J1A/J1B. Three 8-bit RS-170 level video inputs can be used to capture images from three monochrome cameras or one RGB camera. Each channel has sync detection and pixel clock generation to allow simultaneous acquisition from three independent (non-genlocked) sources. Sync and pixel clocks may also be driven from an external RS-422 source. Independent offset and gain controls are available for each of the three channels. Output from the A/D converters can be further processed in the FPGA-based digital front end.

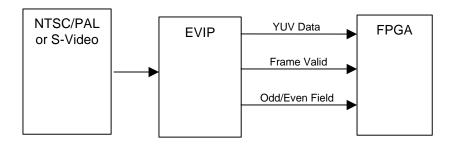

Figure 3. Analog Video Input

#### 1. NTSC/PAL Composite and S-Video Component Input

A Philips SAA7111A Enhanced Video Input Processor digitizes composite or S-video from any source adhering to the NTSC, PAL or SECAM standards for 525-line 59.94 Hz and 625-line 50 Hz video. The chip has four inputs VID1 through VID4 as shown in Table 1. Each input can receive a separate composite video sources, one of which is selected to be sent through the processors. Two S-video sources can be connected (Y on VID1,UV on VID3 or Y on VID2, UV on VID4), one of which is the selected input. These inputs are multiplexed into a common converter (two converters in S-video mode). The primary TriMedia controls the input selection using the I<sup>2</sup>C bus to access the SAA7111A registers.

| J1B Pins | J1B Signal   | Analog In to EVIP | EVIP Input Pin |

|----------|--------------|-------------------|----------------|

| 58, 59   | TAP4_D0, GND | VID1              | Al11           |

| 56, 57   | TAP4_D1, GND | VID2              | Al12           |

| 54, 55   | TAP4_D2, GND | VID3              | Al21           |

| 52, 53   | TAP4_D3, GND | VID4              | Al22           |

Table 1. Composite Analog Video Inputs

The SAA7111A outputs 8-bit parallel digitized video encoded per ITU-R BT.656, which can be directly acquired by the TriMedia processors, or the S3 Virge GX2. The pixel rate is phase locked to the horizontal scan rate of the input image and is nominally 13.5 MHz. Since each pixel requires 16 bits of data, the data output clock rate is 27 MHz. Color video requires three values per pixel. NTSC and PAL use Y (luminance) Cr (red portion of chroma) and Cb (blue portion of chroma). For eight-bit resolution of each component, 24 bits per pixel would be required.

The pixel size of 16 bits (rather than 24 bits) is realized by sub-sampling the chroma portion of the input signal per ITU-R BT.601 (ITU recommendation - broadcast television 601, formerly known as CCIR601) 13.5 MHz 4:2:2 encoding standard. The mnemonic 4:2:2 refers to the fact that for every four pixels, luminance (Y) is sampled four times, while chroma (Cr and Cb) components are only sampled twice. This sub-sampling is in line with the chroma bandwidth limits of the NTSC / PAL standards and does not cause a degradation of picture quality.

#### 2. Monochrome and RGB Analog Video Input

Three 8-bit A/D converters are available for three channels of RS170 compatible monochrome video or one RGB video source in parallel with the EVIP. Each channel has associated sync detection and pixel clock generation to allow simultaneous acquisition from three independent (non-genlocked) sources. Sync and pixel clocks may also be driven from an external RS-422 source. Independent offset and gain controls are available for each of the three channels. Maximum conversion rate (pixel clock) is 80 Mpixels/s.

| Pins           | Signal       |

|----------------|--------------|

| J1A-10, J1A-11 | TAP1-D0, GND |

| J1A-58, J1A-59 | TAP2-D0, GND |

| J1B-10, J1B-11 | TAP3-DO, GND |

Table 2. 8-Bit Analog Input Channels

Output from the A/D converters can be further processed in the FPGA-based front end. Multitap operation is described later in the section on the Front End.

#### C. Digital Input

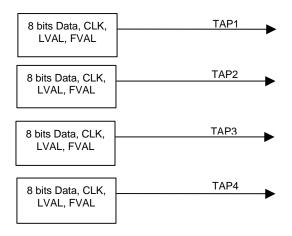

Video capture signals come in through a dual 68-pin VHDCI connector (J1A/J1B). To save pins, analog and digital signals share pins allowing only one or the other for each of the four input taps. Digital video input lines allow direct connection of digital line-scan or area-scan cameras of up to 32 bits.

All digital video data and control signals are differential RS-422 level signals with proper termination for twisted pair cable. High speed line drivers and receivers are used on all digital signals. Industry standard pin-out devices are used for all RS422 receivers and drivers to allow upgrade to faster parts as required. LVDS and PECL interface drivers and receivers are available as selective stuffing options.

Figure 4. Digital Video Input

#### 1. Digital Control Inputs

Four clock inputs (TAP*n\_*PIXCK) come in through the input connector J1A/J1B. These inputs are received by high-speed RS422 differential receivers. The outputs of these receivers go to the crosspoint. PIX\_CLK1 should be used for multi-tap cameras requiring both FPGAs. Programmable clock polarity and input delay allow compensation for clock to data skew.

Eight additional control inputs (TAP*n*\_LVAL and TAP*n*\_FVAL) come in through the Digital input connector J1A/J1B. These inputs are received by high-speed RS422 differential receivers. The outputs of these receivers (LVAL*n*, FVAL*n*) go to the FPGAs; LVAL/FVAL1 and 3 go to both FPGAs, LVAL/FVAL2 and 4 go to FPGA 1 only. These lines may be used for frame valid and line valid signals when attaching multiple cameras.

Four general purpose static inputs (GPIN*n*) are provided. These inputs are received by RS422 differential receivers. The outputs of these receivers go to the UART, where they can be read by the primary TriMedia via the I<sup>2</sup>C bus.

#### 2. Camera Controls

Camera Controls are outputs sent back through the digital input connector J1A/J1B. Three kinds of controls are available: start and exposure signals, master clocks, and general purpose control signals.

#### a) Frame/Line Start and Exposure

Four strobe lines, STROBE1-STROBE4, are output to connector J1A/J1B. These RS422 differential outputs are for line scans or area scans cameras that require a scan start pulse, readout, or exposure control signals (e.g., EXSYNC and PRIN to Dalsa cameras).

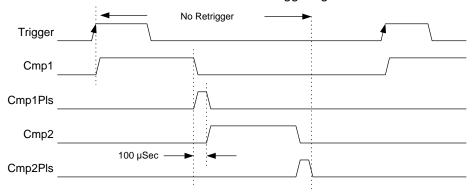

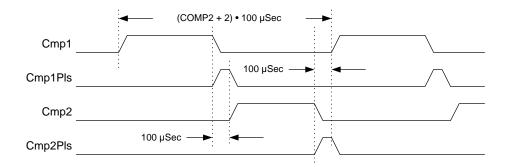

The CPLD has two counters for generating line/frame start and exposure timing signals (Figure 5). These 9-bit counters run at 10 KHz, allowing timing from 100 microseconds to 50 milliseconds. The counters are triggered by the rising edge of one of the two EXT\_TRIG*n* inputs from J1A/J1B. Upon triggering, they count up from zero and stop when they reach maximum count (511). Two 9-bit compare registers, COMP1 and COMP2, are associated with each counter.

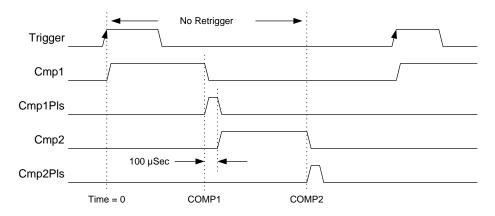

These are programmed to create timing events from 1 to 512 clock cycles after the trigger. In normal usage the value of COMP1 is less than that of COMP2. Four output signals per counter, Cmp1, Cmp1Pls, Cmp2, and Cmp2Pls, are run to the crosspoint where they can be selected to run to the four strobe lines. Signals Cmp1Pls and Cmp2Pls are active high pulses, 100 microseconds wide, beginning at the times programmed in COMP1 and COMP2. Cmp1 is an active high pulse, which starts at the trigger and ends at the time programmed into COMP1. Cmp2 is an active high pulse starting at the time programmed into COMP1 and ending at the time programmed into COMP2 (note that if COMP2 is less than COMP1 this signal will begin during one trigger cycle and end during the next). The counters cannot be retriggered while running until the time programmed into COMP2 has elapsed.

The camera control signals provide a flexible control interface. In a typical application, a Cmp1 signal could be used to start camera exposure. The corresponding Cmp2 signal could initiate transmission of the camera data to the FastImage.

The four external strobe signals on J1A/J1B output the Cmp1 and Cmp2 signals from the two counters. STROBE1 outputs Counter1 Cmp1, STROBE2 outputs Counter1 Cmp2. STROBE3 outputs Counter2 Cmp1, and STROBE4 outputs Counter2 Cmp2.

Figure 5. Camera Control Output Signals

#### b) Master Clocks

Four master clock outputs (MASTER\_CK*n*) to connector J1A/J1B are provided to generate a time base for cameras. These RS422 differential outputs are intended for use with line scan or area scan cameras, which require an external time base. Master clock outputs are generated by the primary and secondary TriMedias using the AI\_OSCLK outputs. Only one clock source is available on the single processor model. These pins can generate any frequency from 1 Hz to 40 MHz in .07 Hz steps using the direct digital synthesizer of the TriMedia. Nominal jitter on these outputs due to digital synthesis is 3.3 nanoseconds. This is reduced to less than 1 nanosecond in the TM1300 when the improved mode is used. In TM1300 improved mode, the frequency resolution is 0.3 Hz.

#### c) General-Purpose Outputs

Four general purpose static outputs (GPOUT0-3) are provided to connector J1A/J1B. These RS422 differential outputs can be written out through the UART by the primary TriMedia (via the  $I^2$ C bus).

#### D. FPGA-Based Front End

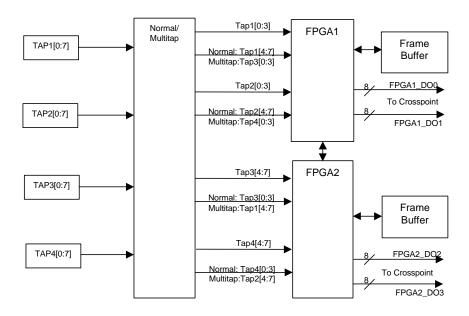

Digital data inputs pass through two FPGAs, each with an external SDRAM. The FPGAs can perform multiplexing and re-order incoming data for Odd/Even and Left/Right tapped cameras. Data is divided into two 16-bit halves, one to each FPGA. When using three or four tap cameras, half the bits from each tap are routed to each FPGA, allowing the two parts to operate identically. When using multiple smaller cameras, each FPGA services a different camera or pair of cameras. These FPGAs are in-system reprogrammable, allowing application-specific operations to be performed.

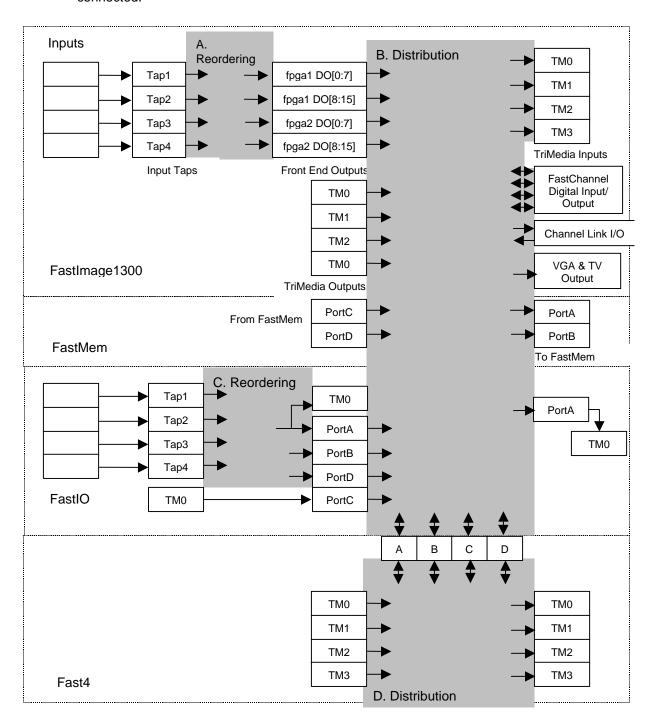

Figure 6. Front End Components and Data Flow

#### 1. FPGA Run States

The input FPGAs control the operation. This section is a general description of the FPGA's capabilities, not specific to any application. The FPGA has two states: stopped and running. When the FPGA is stopped, no data flows in from any source. When the FPGA is running, data flows in from the selected source. The data units can be one of three sizes: pixels, lines, and frames. A Transfer Counter (TC) internal to the FPGA counts the data units as specified in the program.

When the FPGA is stopped, the TC is empty. To change from stopped to running, the program loads a number into the TC. Two running modes are Fixed and Continuous.

- In fixed running mode, the Transfer Counter receives a number of units, and counts down as each pixel, line, or frame is clocked in. When the TC counts down to zero, the FPGA changes back to the stopped state.

- In continuous running mode, the TC receives a maximum initial value, which is also stored in a shadow register. Each time the TC counts down to zero, it is automatically reloaded from the shadow register and running continues.

In both fixed and continuous modes, an end-of-word, end-of-line, or end-of-frame indication is available to the FPGA.

#### 2. Input Signals from Line Cameras to FPGA

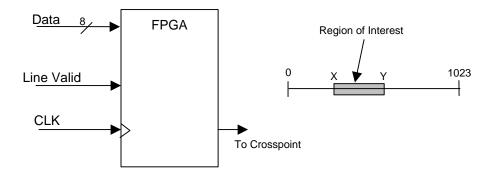

For digital line cameras, the Data, Line Valid, and CLK input signals come directly from the digital input drivers. For analog line cameras, the input data and controls go through the A/D converters to be converted to the Data, Line Valid, and CLK signals for the FPGA. LVAL1, 2, and 3 go to FPGA 1; LVAL1, 3, and 4 go to FPGA2.

A linear region of interest may be specified as begin and end points (X, Y). To accommodate variations in camera timing, the ROI may be specified as a negative value or as a point beyond the upper limit of the line.

Figure 7. Line Camera Input Signals and Region of Interest

#### 3. Input Signals from Frame Cameras to FPGA

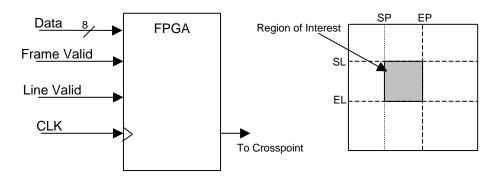

Figure 8. Digital Frame Camera Input Signals and Region of Interest

For digital frame cameras, the Data, Line Valid, Frame Valid, and CLK input signals come directly from the digital input drivers. For analog frame cameras, the input data and controls go through the A/D converters to be converted to the Data, Line Valid, Frame Valid, and CLK signals for the FPGA. LVAL1/FVAL1, 2, and 3 go to FPGA 1; LVAL1/FVAL1, 3, and 4 go to FPGA2.

A rectangular region of interest may be specified as a rectangle with start and end pixels (SP, EP) and start and end lines (SL, EL). To accommodate variations in camera timing, the ROI may be specified using negative values or outside the frame boundaries.

#### 4. NTSC/PAL/S-Video Input Signals

Composite or component video input to the SAA7111 Enhanced Video Input Processor (EVIP) is converted to YUV data that can be processed directly by the TriMedia. The EVIP provides Frame Valid and Odd/Even field signals.

Figure 9. NTSC/PAL/S-Video Input Signals

#### 5. Data Reordering

Data from Multitap cameras is re-ordered using the SDRAM. Incoming data is formed into groups of two 32-bit words inside each FPGA and written to the SDRAM location corresponding to its desired position in the output image. When a complete image has been buffered in the SDRAM, it is read out to the TM1300s while the next image is buffered in the other half of the SDRAM. Four pairs of words are read then four pairs written to reduce the buffering requirements of the FPGA while keeping the SDRAM running near its optimal burst rate.

Depending on the FastImage1300 inputs, the application may require a reordering of the data coming in to the Front End from Taps 1, 2, 3, and/or 4 and exiting the Front End as data bytes FPGA1\_DO[0:7], FPGA1\_DO[8:15], FPGA2\_DO[0:7], and FPGA2\_DO[8:15]. The mapping of input taps to FPGA data bytes is diagrammed in area A of the FastImage1300 crosspoint Figure 14. Each tap can connect to one or more of FPGA1\_DO[0:7] through FPGA2\_DO[8:15]. Multiple input taps can be multiplexed to one FPGA\_DO data byte. Unused taps can be left unconnected.

#### 6. Image Distribution

When the incoming data exceeds the input bandwidth of a single TriMedia processor (80 to 320 MB/s), the images are distributed among multiple processors. One processor receives the first image and the other receives the second image.

Image distribution affects the buffering requirement in the front end. Due to banking restrictions of the SDRAM, multiple frames must be buffered when distributing images to multiple CPUs. Two image buffers are required for each CPU used. Thus when four TM1300s are needed to handle the input bandwidth requirements, eight frames must be buffered. This condition limits the frame size to 1/8 of the frame buffer or 2 megabytes.

#### 7. Data Valid Signals

Four data valid signals are generated by the FPGAs, one for each TriMedia. Each signal is synchronous to the video input clock of the associated TriMedia. Each signal connects to the VI\_DVALID pin of the TriMedia via the crosspoint to match the delay time of the data lines. The data valid signals synchronize the data capture to the valid pixels from the camera in raw capture modes. When using synchronous data buffering in the crosspoint, the position of the data valid relative to the pixel data can be adjusted by varying the number of flip-flop stages each goes through in the crosspoint input buffer. Region of interest capture can be handled in the FPGA if logic cells and routing are available.

Another purpose of the data valid is to pad (or truncate) the frame to a multiple of 64 pixels. This allows use of cameras with non-binary height and width. The 64 pixel limitation comes from the TriMedia, which must define buffers in 64 byte increments. Providing dummy (garbage) pixels at the end of the frame to fill out the buffer greatly simplifies programming in TriMedia raw capture modes. Padding is accomplished with a 6-bit (modulo 64) counter, which runs only when data valid is active. If the contents of the counter are not zero when the next frame sync arrives, data valid is asserted until the counter rolls over to zero. Note that this requires the frame synch signal to precede the first valid pixel by up to 63 clock cycles depending on the number of pixels in a frame. This is not necessary for cameras with a multiple of 64 pixels per frame (most line scan cameras and square format area scan cameras) since the counter will be at zero after the last pixel of the frame.

#### E. Digital Crosspoint Switch

Two Xilinx Virtex XCV50 FPGAs form a switch matrix with flexible I/O buffers at each port. These parts also contain distributed RAM for buffering data as required. Multiplexers can match the input data bus width to the TriMedia processors. Demultiplexers can match TriMedia video output to the digital output bus.

In addition to the main data switch matrix, a smaller switch (I-Cube IQ32B) is used for flexible routing of clock signals with low latency and skew.

Configuration of the crosspoint switch matrix is SRAM-based, allowing reconfiguration in system. Configuration data is downloaded to the part via a standard JTAG port. Because of the relatively slow rate of configuration, the crosspoint switch is used as a static interconnect for most applications. The JTAG bit stream data can be generated by tools available from Xilinx.

The main crosspoint switch is the connection among the sources and destinations. Sources are defined as inputs to the crosspoint:

- Four 8-bit input paths from the FPGAs to the crosspoint.

- Four 8-bit paths from the Video Output of each TriMedia to the crosspoint

- Four 8-bit paths from the FastChannel digital inputs to the crosspoint.

- Three or four 8-bit paths from the FastIO input ports to the crosspoint (when a FastIO is connected). Port A can be set as either input or output; Ports B, C, and D are always inputs to the crosspoint.

- Two 8-bit paths from the FastMem input ports C and D to the crosspoint (when a FastMem is connected).

- Up to four 8-bit paths from the Fast4 input ports to the crosspoint (when a Fast4 is connected.

Destinations are defined as outputs from the crosspoint:

- Four 8-bit paths from the crosspoint to the Video Input of each TriMedia.

- One 16-bit path from the crosspoint to the S3 GX2 for VDA and TV analog outputs

- Four 8-bit paths from the crosspoint to the FastChannel digital outputs.

- One 8-bit path from the crosspoint to the FastIO output port (when a FastIO is connected). Port A must be set as output from the FastImage1300 to the FastIO.

- Two 8-bit paths from the crosspoint to the FastMem output ports A and B (when a FastMem is connected).

Up to four 8-bit paths from the Fast4 input ports to the crosspoint (when a Fast4 is connected.

Figure 10. Main Crosspoint Switch Connections

The mapping of data sources to destinations is diagrammed in area B of the crosspoint diagram above. Any source can connect to one or more destinations. No two sources can be connected to (i.e., drive) the same destination.

The sources and destinations include any PMC daughter cards that are connected to the FastChannel PMC slots. An installed daughter card connects to the data distribution crosspoint switch via one of the two special PMC FastChannel connectors on the FastImage1300; J1 is part of the Front PMC slot and J3 is part of the Rear PMC slot. The connector J3 shares data signals with the Channel Link Input connector.

When a FastChannel PMC daughter card is installed on J3, Channel Link Input lines will be replicated on J3. When Channel Link is installed, a daughter card installed on J3 cannot simultaneously use its FastChannel connection.

The FastChannel I/O signals share 28 lines with the Channel Link Output connector. When Channel Link Output is to be installed, FastChannel cannot be used simultaneously.

If the system includes a FastMem daughter card, Ports A and B are inputs to the FastMem (outputs from the FastImage1300) and Ports C and D are outputs from the FastImem (inputs to the FastImage1300).

If the system includes FastIO daughter card inputs, the application may require a reordering of the data coming in to the FastIO from Taps 1, 2, 3, and/or 4 and exiting the FastIO as FastChannel data ports A, B, C, and D. The mapping of input taps to FastChannel ports is shown in area C of the crosspoint Figure 10 above. Each tap can connect to one or more of PortA, PortB, and PortD. Multiple input taps can be multiplexed to PortA, PortB, or PortD. FastChannel Port A also connects to the video input of the TriMedia processor TM0 on the FastIO board. Any data sent to FastChannel PortA from the FastIO also goes to TM0. Some applications may require the ability to stream data to FastIO TM0 via FastChannel PortA, which acts as an output from the FastImage1300 in this case.

When PortA is used for streaming data from the FastImage1300 to the FastIO, PortA cannot also be connected to any FastIO input taps.

FastChannel PortC is connected to the video output of TM0 on the FastIO.**Port C cannot be connected to any input taps.** Unused taps can be left unconnected.

When one is connected, a Fast4 daughter card provides for distribution of data from any sources to multiple destinations within the board via its central crosspoint switch. The desired mapping of data sources to destinations is diagrammed in area B of the crosspoint Figure 10 above. The sources are the four TriMedia outputs; the destinations include the four TriMedia inputs and the four FastChannel ports, A, B, C, and D. Any source can connect to one or more destinations. No two sources can be connected to the same destination.

## F. <u>Processors and Memory</u>

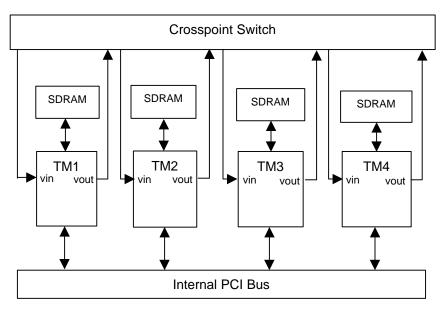

The processors and memory subsystem is diagrammed in Figure 11.

Figure 11. Processors and Memory

#### 1. TriMedia Processors

One to four TriMedia TM1300 processors may be installed on the FastImage card. Processor TM1 is always installed; processors TM2, TM3, and TM4 are optional. The TriMedia has built-in PCI bus interfaces and glueless interface to 8,16, 32 or 64 MB of local Synchronous Dynamic Random-Access Memory (SDRAM) for program and data.

The heart of the TriMedia is a VLIW digital signal processor which can issue up to five instructions in a single clock cycle for up to 900 peak MIPS. Special DSP instructions allow simultaneous operation on four 8-bit or two 16-bit operands in a single instruction. This pushes the peak rate to over 3.3 billion operations per second for 8-bit data.

The TriMedia can issue up to four floating point operations per clock cycle for a peak rate of 720 MFLOPS. The TriMedia does not have floating point multiply/accumulate instructions, but it can issue up to two floating point adds and two floating point multiplies in a single clock cycle.

#### 2. Local SDRAM

Each TriMedia has 8 or 16 megabytes of local SDRAM. The SDRAM is accessible from the host PCI bus (via the bridge) to allow the host to download programs, and (directly) from the secondary PCI bus to allow the TriMedia to transfer data to each other at full PCI bandwidth. All programs to be run in a TriMedia processor must reside in that processor's local SDRAM. The 8-bit Video Input and Video Output from each TriMedia connect directly to the crosspoint.

#### 3. Video Data Paths

Using the large crosspoint switch, any TriMedia can receive video input from the SAA7111A video input processor or from an external analog or digital video source (with or without frame buffering) or directly from one of the PMC modules. In all, up to five video streams can be acquired at one time in the fully loaded configuration, four by the TriMedias and one by the S3 Virge GX2.

Each TriMedia has byte-wide video input and output ports. TriMedia video input ports accept ITU-R BT.656 (formerly CCIR656) encoded 8-bit color data as well as 8- and 10-bit raw data (with sign or zero extend to 16-bits for 10-bit input). When receiving color data in ITU-R BT.656 mode, the incoming data is automatically broken into three components and stored as separate arrays for Y, Cr, and Cb. The maximum video input clock rate is 38 MHz in ITU-R BT.656 mode, or 80MHz in raw mode. TriMedia video output ports can generate ITU-R BT.656 encoded data streams as well as 8-bit raw data. All video input and output data is passed between the port and the TriMedia local SDRAM.

#### 4. Local PCI Bus

Data into and out of the FastImage can use the local PCI bus. High-speed devices connect to the secondary PCI bus via the PMC expansion connectors. Video I/O on the PMC card can use the PCI bus as well as the Video In/Out ports of the baseboard. The TriMedia supports this functionality directly via the image coprocessor unit. When using the onboard S3 SVGA, processed image data can be scaled and alpha blended as well.

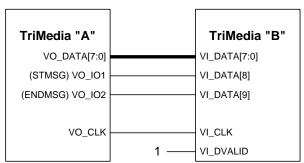

#### 5. Interprocessor Communication

The FastImage board uses the Video In and Video Out units for interprocessor communication as well as video I/O. A special "message passing" mode allows video outputs to connect to video inputs using 8 data bits along with start and stop message bits (Figure 5). In "message passing" mode, the Video Out unit can source data at up to 80 MB/s, and the Video In unit can accept data at up to 80 MB/s. The Video Out unit has a programmable clock generator which can be programmed for byte rates of 4 to 80 MHz. Thus interprocessor link byte rates can be tuned to optimize the bus and SDRAM usage.

Figure 12. Message Passing Connections

Video out/in ports not in use for I/O can tie to other TriMedia processors via the crosspoint switch to form a pipeline using "message passing" mode. This allows DMA data transfer between connected processors at 80 megabytes per second without use of the PCI bus. Independent video input and output modules in the TriMedia allow these data transfers to occur in parallel with DSP CPU operations. Simultaneous DMA transfers can also occur between processors over the secondary PCI bus.

#### 6. Audio Input and Output

TriMedia processors have built-in Audio Input and Output interfaces. These synchronous serial ports are intended for stereo digital audio processing, but can be used as general purpose block DMA devices. Each TM1300 has one audio input AISD1 and four outputs AOSD1, AOSD2, AOSD3, and AOSD4. The AISD1 and AOSD1 lines are from adjacent processors are brought to common connectors along with the corresponding clocks. The output-only lines go to separate connectors, one per processor.

Figure 13. Audio Connections

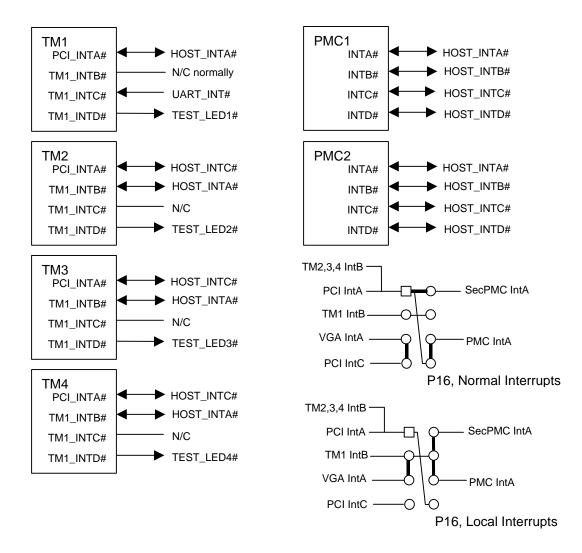

### 7. Interrupts

In the normal configuration, the primary TriMedia TM1 sends and receives HOST\_INTA# from the PCI interface on its PCI\_INTA# pin. The other three TriMedia processors receive HOST\_INTC# on the PCI\_INTA# pin and HOST\_INTA# on the TM1\_INTB# pin, as diagrammed in Figure 14. On the PMC slots, HOST\_INTA# connects to PCI\_INTA#, B to B, C to C, and D to D. Thus, when a daughter card processor interrupts on PMC interrupt line A, it gets back to the Host on the Host's interrupt line A, and so forth. The PMC slots have PCI device numbers 8 and 12, respectively. The S3 has device number 2; the S3 interrupts the Host on HOST\_INTC#. TM1 to TM4 have PCI device numbers 4, 6, 10, and 14, respectively.

Figure 14. Interrupts

Normal interrupts are the default, set by jumpers on P16. Alternatively, P16 can be jumpered for local interrupts; in this configuration, the PMCs and the S3 interrupt TM1 instead of the Host (so that the TriMedia program can handle the interrupt.)

#### 8. TriMedia Configuration EEPROM

Each TriMedia has a small serial EEPROM which contains configuration data (not shown in diagram). Additional configuration data must be loaded by the system BIOS (memory base addresses) and by the run-time software. After a power-on or PCI bus reset, each TriMedia loads clock and ID parameters from the EEPROM. It then stays in a reset state waiting for the host to finish configuration. The TriMedia reads all instructions from the local SDRAM. After a reset, it begins operation starting at the first location in SDRAM. Thus the host is required to load code into each SDRAM before releasing the reset state of the TriMedia. Standard PCI and "Plug and Play" requires the host CPU to assign address bases and other parameters at start-up.

#### 9. Peripheral Controls

Each TriMedia processor can communicate with one of the two front-end FPGAs via the internal I<sup>2</sup>C bus. TM1 and TM2 connect to FPGA1; TM3 and TM4 connect to FPGA2. Interconnections between the FPGAs allow any processor to control either or both FPGAs. The TriMedia can send start, stop, or other messages to the FPGA via this bus.

TriMedia peripherals are controlled by registers located in the MMIO (Memory-Mapped I/O) aperture of each TM1300's address space. The MMIO memory map is shown in figure 3-5 of the TM1300 data book. Individual registers are described in detail in the chapters of their associated peripherals.

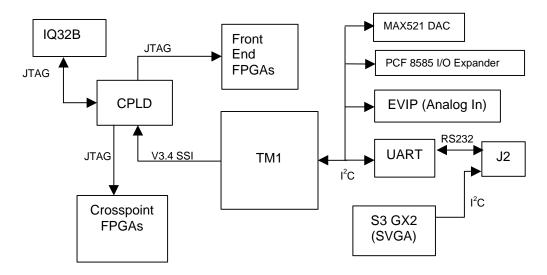

I<sup>2</sup>C peripherals are accessed via the primary TM1300 processor. Devices on the I<sup>2</sup>C bus include the PCF8575 I/O Expander (a 16-bit port to control the FastChannel I/O), the SAA7111A Enhanced Video Input Processor, the MAX521 DAC (used for setting analog video gain and offset), and the UART. All I<sup>2</sup>C peripherals on the FastImage use 7-bit addressing. The PCF8575 is accessed at 0x40 for writing and 0x41 for reading. The SAA7111A is accessed at 0x48 for writing and 0x49 for reading; its internal registers are described in the data sheet section 17. The MAX521 is accessed at 0x50 for writing and 0x51 for reading. The UART is accessed at 0x54 for writing and 0x55 for reading. The I<sup>2</sup>C bus is discussed further in Programming, Configuration and Test below.

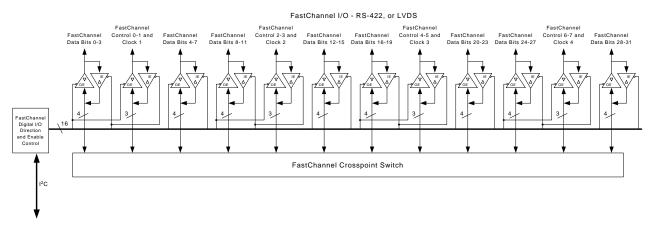

#### G. FastChannel Digital Input/Output

The bi-directional Fast-Channel I/O interface provides 32 bits of differential RS422 or LVDS compatible I/O. Signal direction is programmable in groups of 4 bits. In addition to the 32 data signals, 8 control signals and 4 clocks are grouped into four sets of two control signals plus one clock. The direction of each of these control signal groups is linked to the direction of the low nibble of each byte as shown in the block diagram below.

Figure 15. FastChannel Input/Output

At the lowest level, the drivers and receivers are controlled by active low output enables and input enables. At power on all enable signals are inactive (high). Software should maintain a direction and enable bit for each I/O group. Calls to the API function to update these values should cause the bits to be translated into input and output enables and the updated values to be written to the I<sup>2</sup>C registers. Translation from direction and enable to input enable/output enable is shown in the table below.

| Direction | Enable   | Output Enable (Port 0) bit | Input Enable (Port 1) bit |

|-----------|----------|----------------------------|---------------------------|

| In        | Enabled  | 1                          | 0                         |

| In        | Disabled | 1                          | 1                         |

| Out       | Enabled  | 0                          | 1                         |

| Out       | Disabled | 1                          | 1                         |

Table 3. FastChannel Interface Controls

The I<sup>2</sup>C registers are implemented using a Philips PCF8575 16-bit I/O expander. Ports are written at I<sup>2</sup>C address 0x40 using multiple byte write. Data is transferred to the output of the PCF8575 after the second byte of data is written. Thus all 16 input and output enables are updated simultaneously.

The first byte of data after the I<sup>2</sup>C address byte is the driver output enables. The PCF8575 data sheet refers to this as Port 0. All driver output enables are active low, i.e. writing a zero turns the drivers on. The second byte of data after the I<sup>2</sup>C address byte is the receiver input enables. The PCF8575 data sheet refers to this as Port 1. All receiver input enables are active low, i.e. writing a zero turns the receivers on. The bit layout of each register is the same as shown inTable 4.

Any enabled inputs can potentially fight with the crosspoint switch if the switch is not properly configured. A safe approach to enabling FastChannel I/O is to disable all inputs and outputs while downloading the FPGAs.

Signal direction is not intended to be dynamic. Direction should be specified in the digital output profile, either as an 8-bit entry or 8 individual 1-bit entries. Enables may also be specified in the "digital output" profile, however there should also be an API function to enable or disable I/O using an 8-bit mask. If not specified in the profile, signals should remain disabled until the API function is called.

| Bit: | FastChannel I/O Data / Control Bits Affected: |

|------|-----------------------------------------------|

| 0    | D0-D3, C0, C1, CLK1                           |

| 1    | D4-D7                                         |

| 2    | D8-D11, C2, C3, CLK2                          |

| 3    | D12-D15                                       |

| 4    | D16-D19, C4, C5, CLK3                         |

| 5    | D20-D23                                       |

| 6    | D24-D27, C6, C7, CLK4                         |

| 7    | D28-D31                                       |

Table 4 I/O Expander Registers

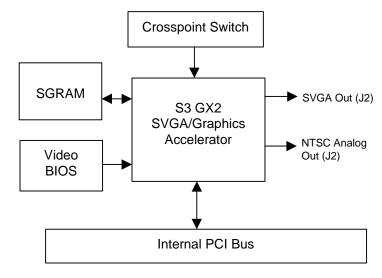

#### H. Analog Output

The S3 Virge GX2 2D/3D accelerator provides standard SVGA output at resolutions up to 1280 by 1024 pixels and 72 Hz frame rates (non-interlaced). It also provides an NTSC / PAL compatible monitor output for 525-line 59.94 Hz and 625-line 50 Hz video.

Figure 16. Analog Output

The S3 accelerator utilizes a 64Kx8 bit EPROM for video BIOS as well as program memory space. This device shares a portion of the memory interface during boot-up. After the device has come up and been configured, the EPROM pins go tri-state and the SGRAM has control of the bus.

Any TriMedia processor can send its video output to the S3 VGA adapter. This allows direct NTSC or PAL video output without a PMC module. Alternately, the S3 can be used to acquire video from an external source.

Three 0 to 1V RGB outputs (plus TTL level synch signals) drive a standard SVGA computer monitor. SVGA monitor signals go out through a 68-pin high-density connector (J2) requiring use of Alacron monitor cables.

Two RS-170 level outputs provide either composite video (NTSC or PAL) or S-video to drive a standard television monitor. Composite and S-video outputs share connector J2 with the SVGA outputs and the RS-232 port.

#### I. PCI-PCI Bridge

A Digital Semiconductor (Intel) 21150 PCI bridge chip isolates on-board components from the host PCI bus while allowing a transparent data path between the host and on-board secondary PCI buses. This chip conforms to the PCI specification for bridges and is supported by most BIOSs.

While the bridge chip presents a single electrical load to the host PCI bus, the four TriMedia processors, SVGA adapter and PMC modules look like as many as seven devices to the host system BIOS. The PCI standard allows each device behind a bridge to have its own configuration space, and the PCI BIOS code sets up these devices individually.

The 21150 bridge chip has configuration space registers which are described in the data book chapter 14. Many of these registers are standard for all PCI to PCI bridges and should be handled by the system BIOS. Registers which must be handled by Alacron software are listed in section 14.2 "Device-Specific Configuration Registers." Of these, the "Secondary Clock Control Register" is loaded by on-board hardware. Most of the other registers are left in their default states.

#### J. PMC Slots

The FastImage incorporates two 32-bit PCI Mezzanine Card (PMC) slots. The first PMC slot (PMC1, connectors P1/ P2) connects the FastIO or any single-width standard length PMC module to the FastImage internal PCI bus with access to the rear I/O connector panel on the PC chassis. The corresponding PMC FastChannel connector (J1 on the board) provides a direct connection to the crosspoint switch on the FastImage.

The second PMC slot (P6/P7) is available for boards with no requirement for I/O panel space. This slot is intended for adding TriMedia processors or memory. The corresponding PMC FastChannel connector (J3 on the board) provides a direct connection to the crosspoint switch on the FastImage.

NOTE: The data pins on PMC2 FastChannel connector J3 are shared with the Channel Link digital input signals. This connector can be used for communication with the daughter card only when digital input from the Channel Link interface is installed.

#### K. CPLD

A Complex Programmable Logic Device (CPLD) provides some camera control and board interface logic. The primary TriMedia processor communicates with this device via its V.34 synchronous serial interface. The CPLD provides logic to convert the V.34 serial data to a JTAG stream for programming the main and clock crosspoint switches and to a Xilinx standard serial stream for programming the FPGAs. This device also provides variable time delays for camera and strobe control. The CPLD is downloaded from a serial EPROM each time the system is started. See Programming, Configuration, and Test, and the CPLD Specification later in this manual for details.

#### L. UART and Serial Port

A simple RS-232 UART is provided for camera setup and low speed control. It supports baud rates from 600 to 19,200. Although a host serial port could be used for this, having the UART on board can simplify deliverable software.

The primary TriMedia processor communicates with the UART via I<sup>2</sup>C (the Inter-Integrated Circuit 2-wire serial bus). The UART provides transmit and receive data, as well as one handshake input and one handshake output. The handshake lines are under program control. They typically tie to Data Terminal Ready and Data Set Ready lines of the remote equipment.

The UART is accessed at I<sup>2</sup>C address 0x54 for writing and 0x55 for reading. In addition to serial data input and output registers it has several I/O bits which can be accessed at different sub addresses. Its internal registers are described in the UART Specification later in this manual.

#### M. Power

The FastImage1300 on-board power supply provides the following DC/DC conversions:

- +3.3V @ 5A (16.5W) typ.

- +2.5V @ 4A (10W) typ.

Power connectors P5 and P13 supply additional +5V current using two Alacron 10024-00160 power cables. P5 also supplies +3.3V power from an external source to the APMC (inboard) slot. P13 also supplies +3.3V to the PMC1 (outer) slot.

## N. Clock Distribution

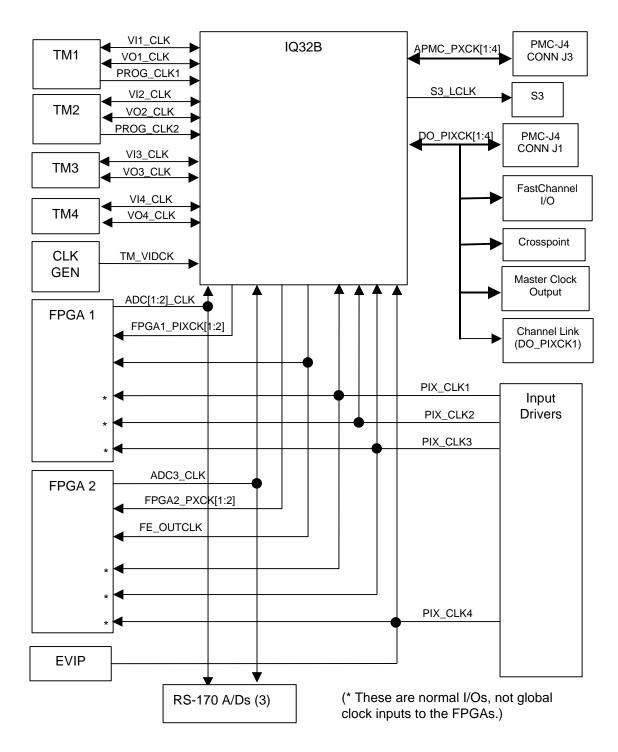

The IQ32B crosspoint switch distributes the clock signals to the FastImage components as shown in Figure 17.

Figure 17. IQ32B Clock Distribution

#### 1. IQ32B Pins, Ports, and Signals

Table 5 shows the signals to and from the IQ32B pins.

| Port No. | Phys Pin<br>No. | Signal            | Direction/Connection                                                                       |

|----------|-----------------|-------------------|--------------------------------------------------------------------------------------------|

| P000     | 49              | VI1_CLK           | To/From TM1                                                                                |

| P001     | 48              | VI2_CLK           | To/From TM2                                                                                |

| P002     | 46              | VI3_CLK           | To/From TM3                                                                                |

| P003     | 45              | VI4_CLK           | To/From TM4                                                                                |

| P004     | 43              | VO1_CLK           | To/From TM1                                                                                |

| P005     | 42              | VO2_CLK           | To/From TM2                                                                                |

| P006     | 41              | VO3_CLK           | To/From TM3                                                                                |

| P007     | 38              | VO4 CLK           | To/From TM4                                                                                |

| P008     | 37              | PROG_CLK1         | From TM1                                                                                   |

| P009     | 36              | PROG_CLK2         | From TM2                                                                                   |

| P010     | 35              | PIX_CLK1          | From Input Receivers                                                                       |

| P011     | 32              | PIX_CLK2          | From Input Receivers                                                                       |

| P012     | 30              | PIX_CLK3          | From Input Receivers                                                                       |

| P013     | 29              | PIX_CLK4/EVIP_LLC | From Input Receivers or 7111A                                                              |

| P014     | 28              | ADC1_CLK          | From FPGA1 to RS-170 ADC1                                                                  |

| P015     | 24              | TM_VIDCK          | From Clock Generator                                                                       |

| P016     | 23              | APMC_PXCK1        | To/From PMC-J4 Connector J3                                                                |

| P017     | 21              | APMC_PXCK2        | To/From PMC-J4 Connector J3                                                                |

| P018     | 20              | APMC_PXCK3        | To/From PMC-J4 Connector J3                                                                |

| P019     | 18              | APMC PXCK4        | To/From PMC-J4 Connector J3                                                                |

| P020     | 17              | FE_OUTCLK         | To FPGA1 and FPGA2                                                                         |

| P021     | 16              | FPGA1_PXCK1       | To FPGA1                                                                                   |

| P022     | 13              | FPGA1_PXCK2       | To FPGA1                                                                                   |

| P023     | 12              | FPGA2_PXCK1       | To FPGA2                                                                                   |

| P024     | 11              | FPGA2_PXCK2       | To FPGA2                                                                                   |

| P025     | 10              | DO_PXCK1          | From I/O Drivers, To Channel Link, To FastChannel,<br>To Crosspoint Switch, To MCLK Output |

| P026     | 9               | DO_PXCK2          | From I/O Drivers, To FastChannel, To Crosspoint Switch, To MCLK Output                     |

| P027     | 6               | DO_PXCK3          | From I/O Drivers, To FastChannel, To Crosspoint<br>Switch, To MCLK Output                  |

| P028     | 5               | DO_PXCK4          | From I/O Drivers, To FastChannel, To Crosspoint<br>Switch, To MCLK Output                  |

| P029     | 3               | S3_LCLK           | To S3 GX2                                                                                  |

| P030     | 2               | ADC3_CLK          | From FPGA2 to RS-170 ADC3                                                                  |

| P031     | 1               | ADC2_CLK          | From FPGA1 to RS-170 ADC2                                                                  |

Table 5. IQ32B Signals

Using the IQ32B crosspoint, any of these clock signals can be connected to any other. Each signal going through the crosspoint can be specified as an input, output, forced low, or forced high signal. The input/output direction corresponds to the source of the clock. Signals may be forced to low or high in the crosspoint.

#### a) VI[1:4]\_CLK and VO[1:4]\_CLK

The VI[1:4]\_CLK signals clock the video input data into the TriMedia, while the VO[1:4]\_CLK signals clock the video output data out of the TriMedia. Both these clocks can be generated and driven out by the TriMedia, or received as inputs from the IQ32B. Normally, the Video Input clocks are connected via the IQ32B to some other clock signal and sent to the TriMedia, while the Video Output clocks are sourced by the TriMedia

#### b) PROG\_CLK[1:2]

PROG\_CLK1 and PROG\_CLK2 are the Audio input over sampling clocks from the TriMedia. They are spare clock sources programmable from 1 HZ to 40MHZ in increments of 0.3HZ.

#### c) PIX\_CLK[1:4]

The PIX\_CLK[1:4] signals are the master pixel clock for input data from the four taps. These clocks are driven by the Digital Input taps, and some Analog line scan cameras provide digital clocks. The PIX\_CLK[1:4] signals are connected on the FastImage board to the FPGAs and the EVIP. FPGA1 receives PIX\_CLK[1:3], while FPGA2 receives PIX\_CLK[1, 3, and 4]. For Analog input, the EVIP drives PIX\_CLK4.

#### d) ADC[1:3] CLK

The ADC[1:3]\_CLK clocks connect to the A/D converters. Some analog cameras provide an external clock; this external clock is sent to the A/Ds via the crosspoint. Other analog cameras generate only VSYNC and HSYNC, and for these the Front End FPGAs generate the ADC[1:3]\_CLK clocks. Some multi-tap analog cameras provide an external clock only on the first tap; this clock may be sent to all three ADCs.

#### e) TM\_VIDCK

The Clock Generator (a CY2292 part) generates TM\_VIDCK, which can serve as a Master Clock. TM\_VIDCK is jumper-selectable; see the chapter Connectors and Jumpers for details on the available speeds.

#### f) APMC\_PXCK[1:4]

The pixel clocks for the PMC connector J3, APMC\_PXCK[1:4], can be generated by TriMedia on the PMC daughter card connected to J3, or can be tied via the IQ32B to clocks originating on the FastImage.

#### g) FPGA[1:2]\_PIXCK[1:2] and FE\_OUTCLK

FPGA1 receives two general-purpose pixel clocks, FPGA1\_PIXCK1 and FPGA1\_PXCK2, and a shared clock, FE\_OUTCLK, commonly used to clock data between the FPGAs and the TMs. FPGA2 receives two general-purpose pixel clocks, FPGA2\_PIXCK1 and FPGA2\_PXCK2, and the shared clock, FE\_OUTCLK.

#### h) DO\_PIXCK[1:4]

DO\_PIXCK[1:4] is the clock for FastChannel digital I/O as well as for processors on PMC connector J1. DO\_PIXCK[1:4] can be generated by the FastChannel input or by TriMedia on the PMC daughter card connected to J1, or can be tied via the IQ32B to clocks originating on the FastImage. In addition, DO\_PIXCK[1:4] is connected on the FastImage board to the FastChannel I/O, the Master Clock output, and the main crosspoint switch. DO PIXCK1 connects to the Channel Link interface.

#### i) S3\_LCLK

S3 LCLK is the Local Peripheral Bus (LPB) clock to the S3 GX2 VGA chip.

## III. CONNECTORS AND JUMPERS

#### A. Connectors

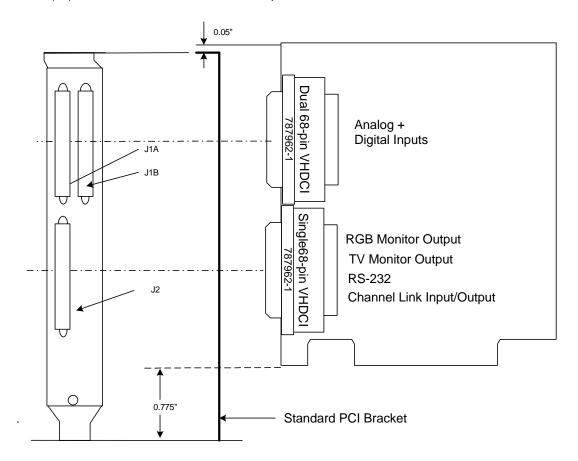

#### 1. Rear Bracket Connectors

Digital/Analog Input Connectors (J1A/J1B) and NTSC/RS232/VGA/Channel Link I/O Connector (J2) are accessible from the PCI rear panel bracket.

Figure 18. FastImage1300 Front Panel Bracket

## 2. Analog and Digital Input Connector (J1A/J1B)

The Analog and Digital Input connector is on the Rear PCI Bracket: JA1/J1B is a Dual 68-Pin Connector, with 32-bit Digital Inputs and Control or Analog Inputs (Table 6). Digital signals are differential, consisting of a positive and a negative signal pair; in the table, they are combined (e.g., differential signals TAP1\_LVALP and TAP1\_LVALN\* are shown as just TAP1\_LVAL). The positive signal is always the lower-numbered pin in each pair; the negative signal is the higher-numbered pin. Analog signals connect to the lower-numbered pins with return on the higher-numbered pins.

| J1A/J1B<br>Pins | J1A Signal                         | J1B Signal                         | J1A/J1B<br>Pins | J1A Signal                         | J1B Signal                                      |

|-----------------|------------------------------------|------------------------------------|-----------------|------------------------------------|-------------------------------------------------|

| 1,2             | TAP1 LVAL                          | TAP3 LVAL                          | 35, 36          | STROBE 1                           | STROBE 3                                        |

| 3, 4            | TAP1 FVAL                          | TAP3 FVAL                          | 37, 38          | STROBE 2                           | STROBE 4                                        |

| 5, 6            | TAP1 PXCK                          | TAP3 PXCK                          | 39, 40          | MASTER CK1                         | MASTER CK3                                      |

| 7, 8            | GPIN1                              | GPIN3                              | 41, 42          | MASTER_CK2                         | MASTER_CK4                                      |

| 9               | GND                                | GND                                | 43              | GND                                | GND                                             |

| 10, 11          | TAP1_D0<br>Analog RS170<br>Input 1 | TAP3_D0<br>Analog RS170<br>Input 3 | 44, 45          | TAP2_D7                            | TAP4_D7                                         |

| 12, 13          | TAP1_D1                            | TAP3_D1                            | 46, 47          | TAP2_D6                            | TAP4_D6                                         |

| 14, 15          | TAP1_D2                            | TAP3_D2                            | 48, 49          | TAP2_D5                            | TAP4_D5                                         |

| 16, 17          | TAP1_D3                            | TAP3_D3                            | 50, 51          | TAP2_D4                            | TAP4_D4                                         |

| 18, 19          | TAP1_D4                            | TAP3_D4                            | 52, 53          | TAP2_D3                            | TAP4_D3 Analog Composite 4, S-Video C2          |

| 20, 21          | TAP1_D5                            | TAP3_D5                            | 54, 55          | TAP2_D2                            | TAP4_D2 Analog Composite 3, S-Video C1          |

| 22, 23          | TAP1_D6                            | TAP3_D6                            | 56, 57          | TAP2_D1                            | TAP4_D1<br>Analog<br>Composite 2,<br>S-Video Y2 |